High Bandwidth Connectors for New Technologies

The world is fast and dynamic, as are today’s devices. There is a constant quest to develop modern applications which exceed the speed limits of their predecessors. Nowhere is speed more of a design concern than for connectors. Connectors are getting smaller and denser while handling faster speeds. Smart applications and intelligent environments abound with high bandwidth connectors. From 56G to 112G to 224G, the connector industry strives to meet the challenges put forth by new technologies every day.

Among the many challenges we are facing, one of the most prominent is that of maintaining a 224Gb/s performance with manufacturing tolerances not only limited to the connector, but throughout the PCB and the whole system. The tolerances for the connectors and breakout regions are limited by the PCB process technology, but there are factors that need to be addressed in the design. This can range from feature alignment, signal pad connector wipe and tolerance regions, back drill stub depth, and board perimeter routing tolerances. Additionally, with increased density, there is a significant chance that signal interference and crosstalk will be higher.

Apart from these, the importance of controlling impedance cannot be stressed enough. Even the slightest mismatches in impedance can lead to signal loss at high frequencies, which in turn will bring the performance of the application upside down. Furthermore, with increased signal density and data rates, the power density also spikes, increasing heat levels significantly, leading to thermal and cooling issues and related challenges.

Other significant factors include return loss, effective return loss, insertion loss, and crosstalk, which influence many metrics. According to Michael Rowlands, SI Engineering Manager at Amphenol, “Crosstalk and skew performance in-board with a breakout region (BOR) will be the make-or-break feature of 224 Gb/s interconnect designs and channel performance.” Also, the design of the test fixture used with the connector is important, as we want that test fixture to have no noise or reflection.

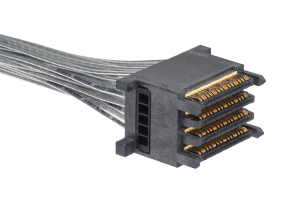

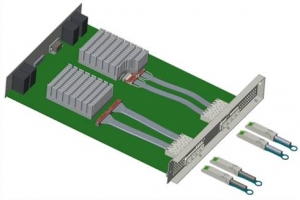

Amphenol DensiLink 200G per lane; 1.6T aggregate bandwidth Amphenol DensiLink 200G per lane; 1.6T aggregate bandwidth |

In order to analyze how the connector will interface with its board stack and pad stack, and to have an idea of its performance, designers always prefer good mechanical models of connectors to bring into the simulation.

14 GHz or 28 Gb/s should be defined as the cutoff point for any connector model. Above that bandwidth/data rate, it is critical to model the connector and the PCB together. A connector with crosstalk resonance cannot be modeled correctly unless the PCB is included in the model at the same time.

To protect the intellectual property of their design, connector manufacturers often provide encrypted mechanical models of their products for integration into the simulation. However, their accuracy is quite often questioned. Rowlands notes that it is standard for Amphenol to provide simulated S-parameters. Measured models are also available, but they often have causality and noise imperfections that make it difficult to analyze in a channel. Engineers can use Amphenol’s models in any tool that reads S-parameters, such as Matlab, ADS, ANSYS, and various free download tools, for incorporation into their simulation.

In short, irrespective of the design, to deliver optimal signal integrity, it is crucial to consider the area immediately leading up to the connector. Simulating the connector with the PCB along with considering every other factor leading up to the connector is essential to get the best results.

Industry-leading manufacturers like Amphenol offer high bandwidth connectors with essential support materials, guidelines on using simulation tools, breakout recommendations, and technical support to ensure an optimal design.

Check out Amphenol’s high bandwidth connectors to learn more.